## SPEED

**Resource-Efficient and High-Performance**

**Deployment for Data Plane Programs**

Haifeng Zhou, Chunming Wu

### Xiang Chen, Hongyan Liu, Qun Huang, Peiqiao Wang, Dong Zhang,

### Monitor

### Security

### Routing

Background | Problems | Challenges | Design | Evaluation | Summary

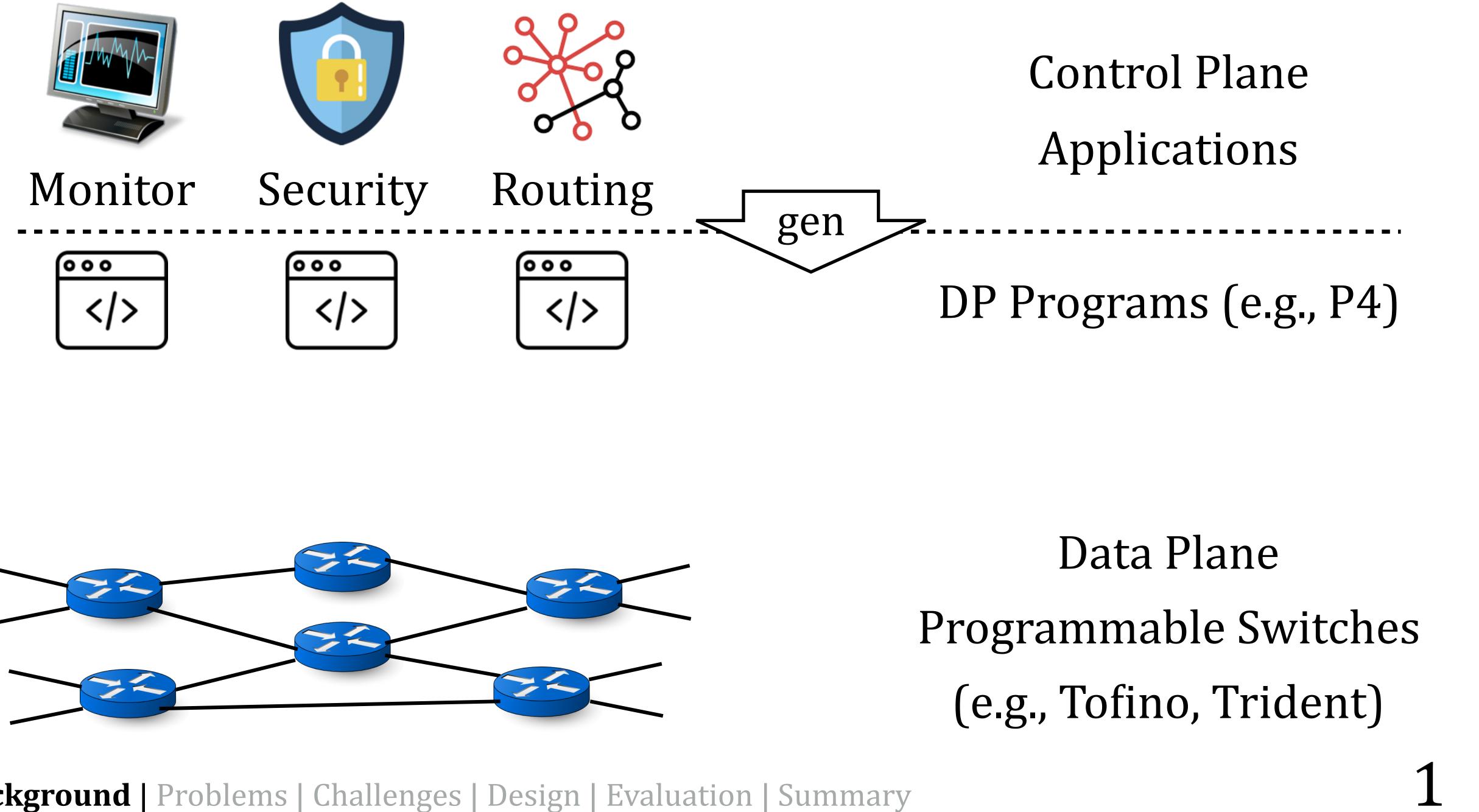

## Control Plane Applications

## Data Plane Programmable Switches (e.g., Tofino, Trident)

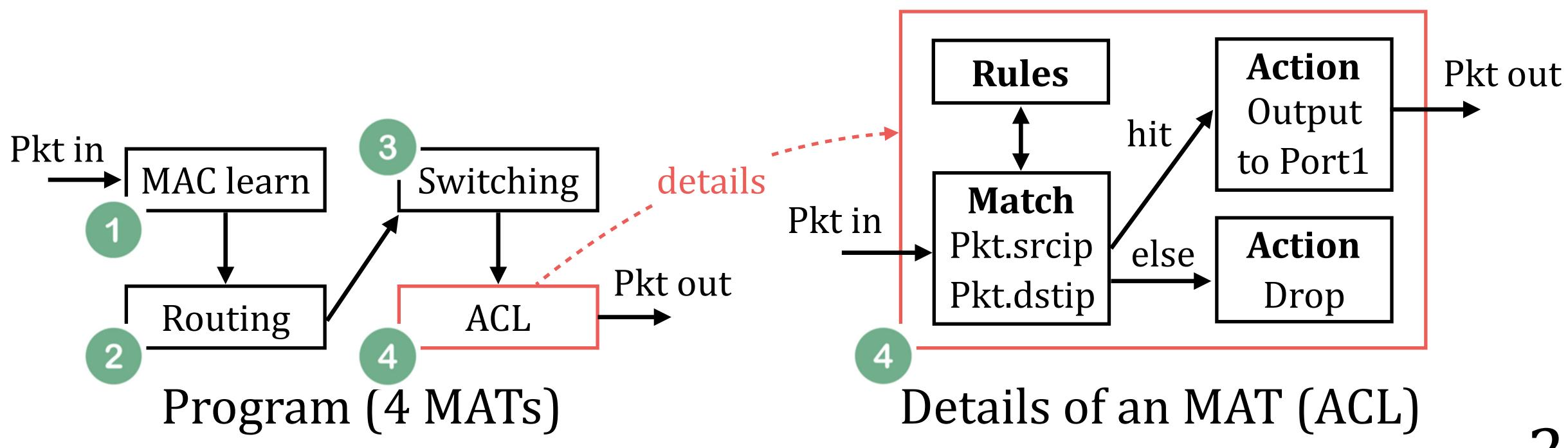

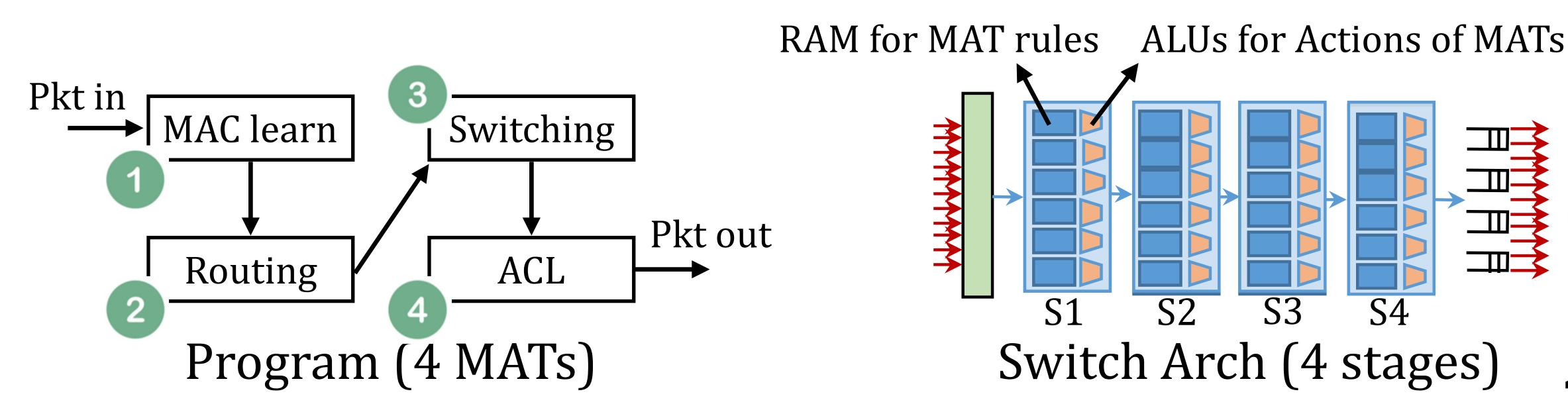

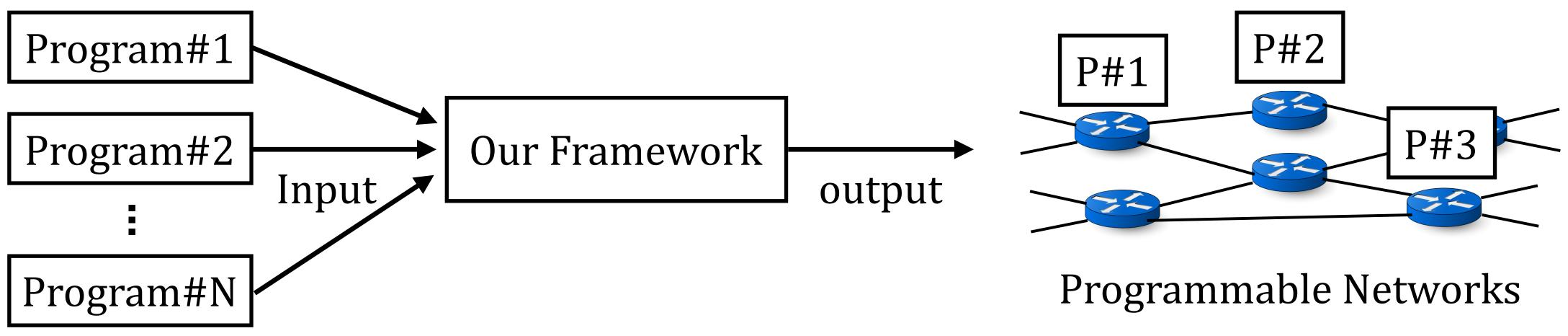

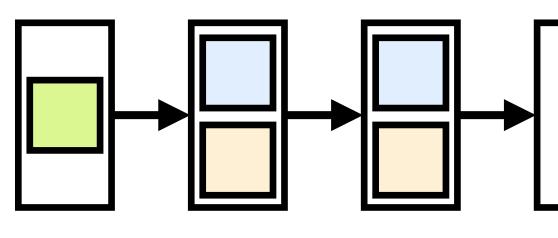

# **Data Plane Program Deployment Input**: data plane programs w/ match action tables (MATs)

# **Data Plane Program Deployment Input**: data plane programs w/ match action tables (MATs)

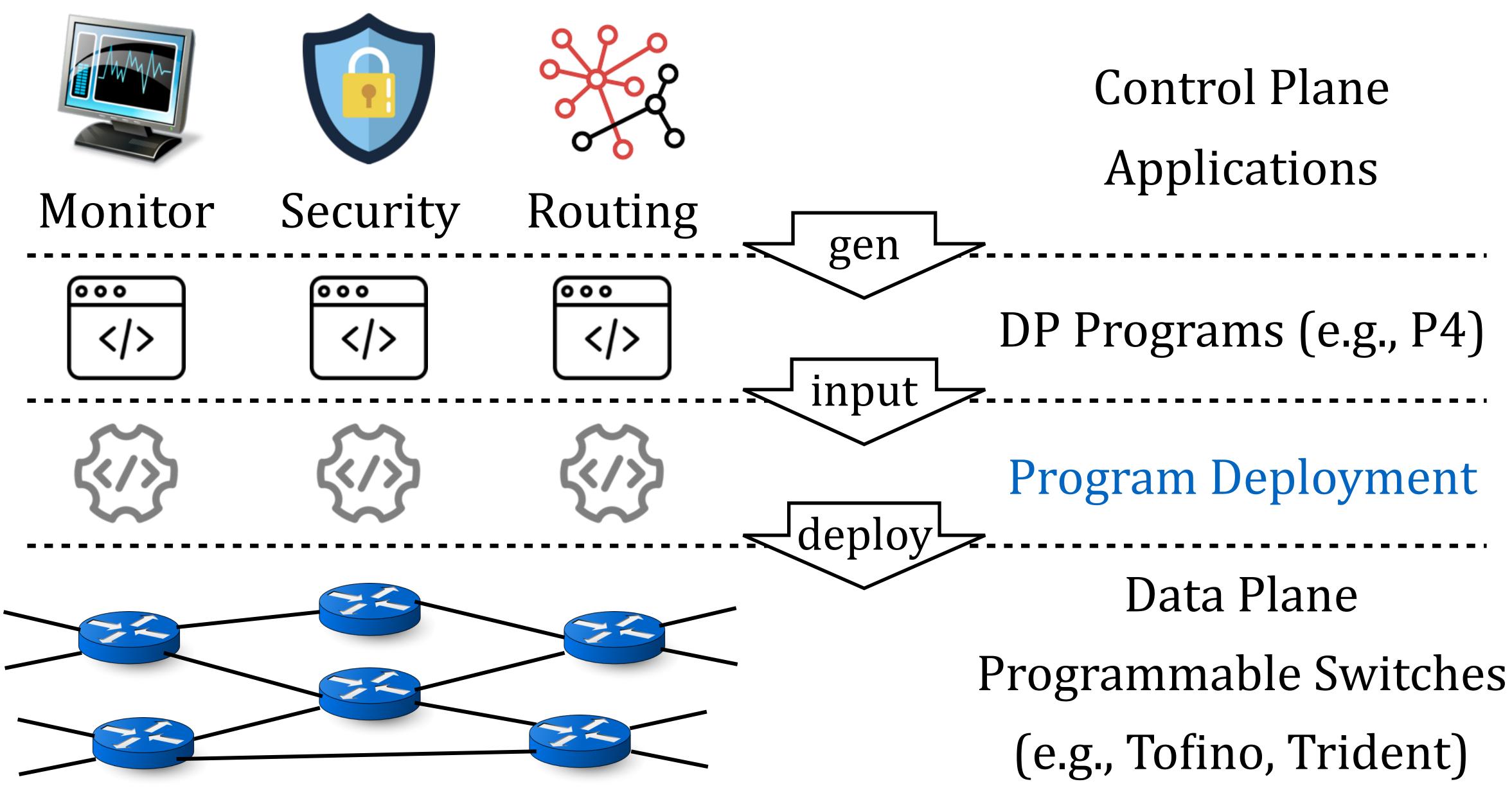

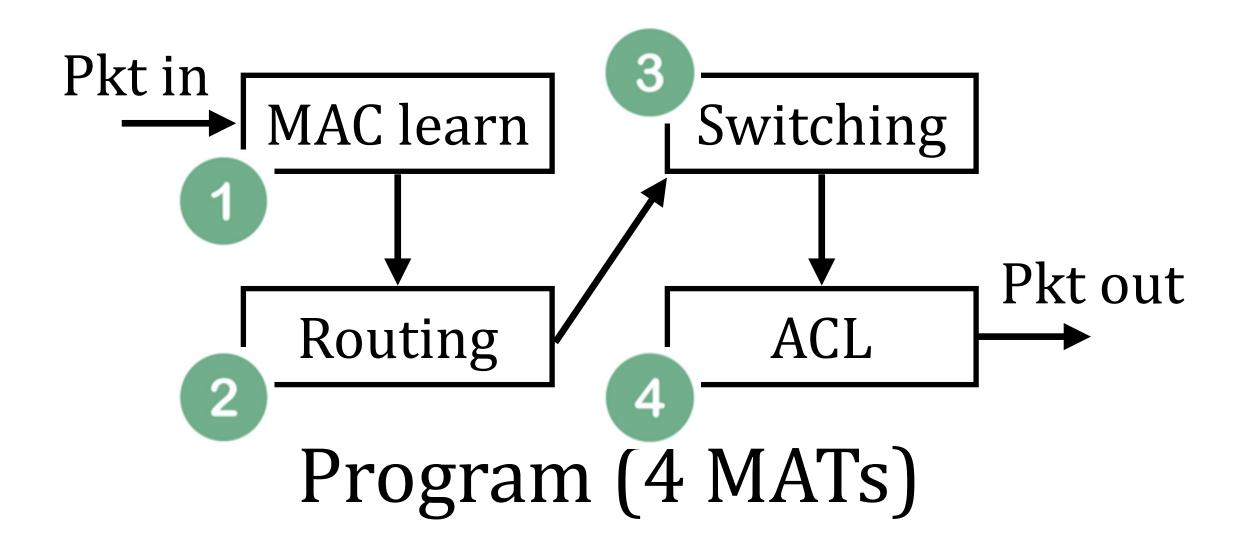

## **Data Plane Program Deployment**

**Input**: data plane programs w/ match action tables (MATs)

**Target**: programmable switches w/ switch stages

# **Data Plane Program Deployment Input**: data plane programs w/ match action tables (MATs) **Target**: programmable switches w/ switch stages **Output:** Mapping between an MAT and a stage

# **Data Plane Program Deployment Input**: data plane programs w/ match action tables (MATs) **Target**: programmable switches w/ switch stages **Output:** Mapping between an MAT and a stage Enable deployment of advanced network applications (1) Software-defined measurement: FlowRadar, Martini, PINT, OmniMon, etc.

(3) Traffic scheduling and optimization: PIFO, PIEO, HPCC, P4air, etc.

- (2) In-network acceleration: NetCache, NetChain, NetLock, Cheetah, etc.

## **Requirements of Program Deployment**

- Given *multiple* input data plane programs:

- simultaneously deploy these programs on network

- 1. Resource efficiency

- given that switch resources are limited (e.g., <10 MB memory)

- 2. High end-to-end packet processing performance satisfy tight latency/throughput requirements issued by apps

## **Limitations of Existing Solutions**

(2) Virtualization: Hyper4 (CoNEXT'16), P4Visor (CoNEXT'18), etc.

Background | **Problems** | Challenges | Design | Evaluation | Summary

### (1) Compiler design: RMT (NSDI'15), dRMT (SIGCOMM'17), etc.

## **Limitations of Existing Solutions**

(2) Low performance due to lack of considering constraints

- (1) Compiler design: RMT (NSDI'15), dRMT (SIGCOMM'17), etc.

- (2) Virtualization: Hyper4 (CoNEXT'16), P4Visor (CoNEXT'18), etc.

- Support program deployment on a *single* programmable switch

- (1) Poor resource efficiency as scaling to multiple programs

- - (device connectivity, traffic routing, etc.)

## Goal

Provide program deployment that achieves:

(2) High Performance: low latency and high throughput

- (1) **Resource Efficiency**: make the best use of switch resources

## Challenges

Background | Problems | Challenges | Design | Evaluation | Summary

(1) Program diversity: case-by-case analysis and deployment e.g., Count-Min (sequential layout), NetCache (branch-heavy)

## Challenges

(1) Program diversity: case-by-case analysis and deploymente.g., Count-Min (sequential layout), NetCache (branch-heavy)

(2) Heterogeneous constraints: complicated problem solving switch resource limitations vs. network-wide constraints (e.g., device connectivity)

## Challenges

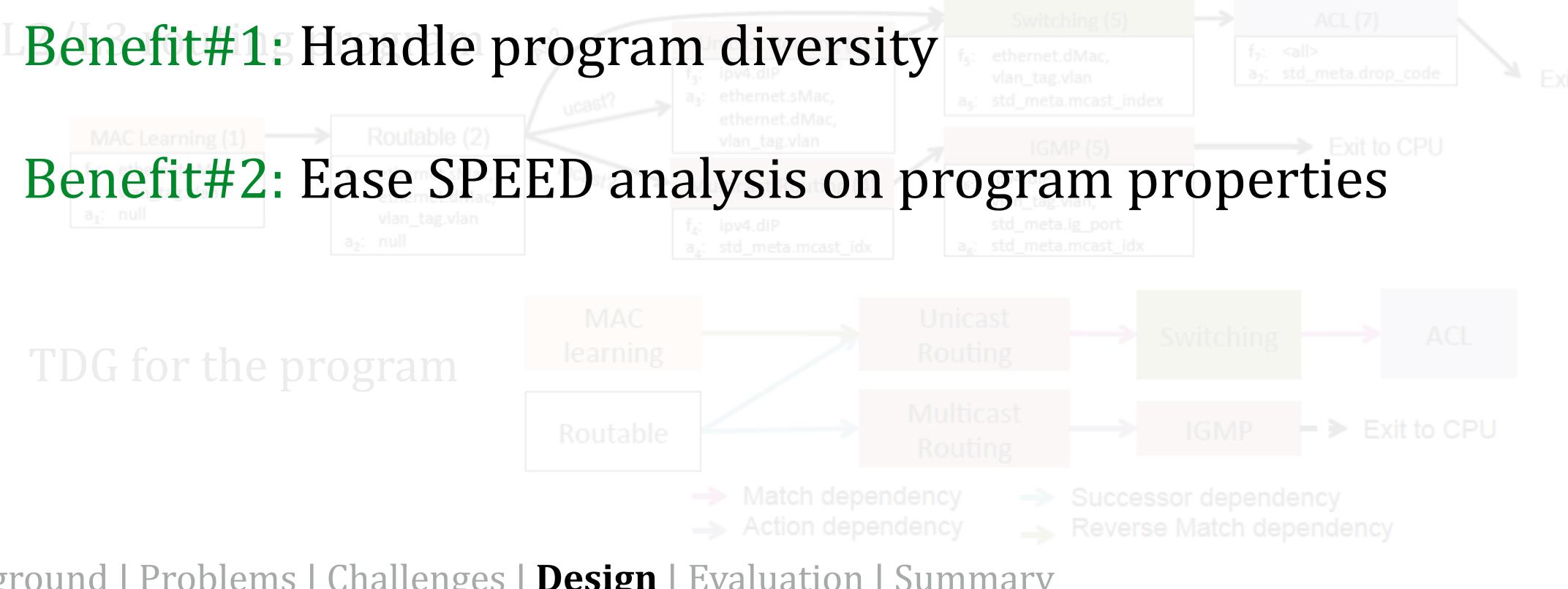

(1) **Program diversity:** case-by-case analysis and deployment e.g., Count-Min (sequential layout), NetCache (branch-heavy)

switch resource limitations vs. network-wide constraints (e.g., device connectivity) to preserve original packet processing semantics

(2) Heterogeneous constraints: complicated problem solving (3) Inter-device coordination: pkt scheduling among switches

### **SPEED Framework**

(1) Table dependency graph for program diversity

(2) Program merging for achieving resource efficiency(3) One big switch for heterogeneous constraints

(4) Inter-device packet scheduling for device coordination

### **SPEED Framework**

(1) Table dependency graph for program diversity

(2) Program merging for achieving resource efficiency (3) One big switch for heterogeneous constraints

(4) Inter-device packet scheduling for device coordination

Background | Problems | Challenges | **Design** | Evaluation | Summary

This Talk

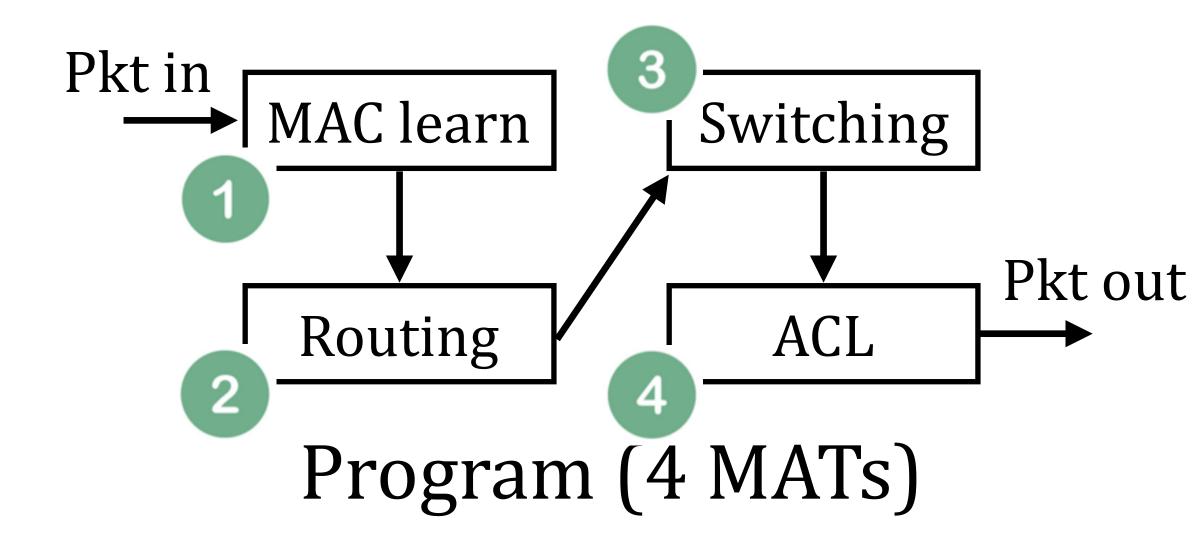

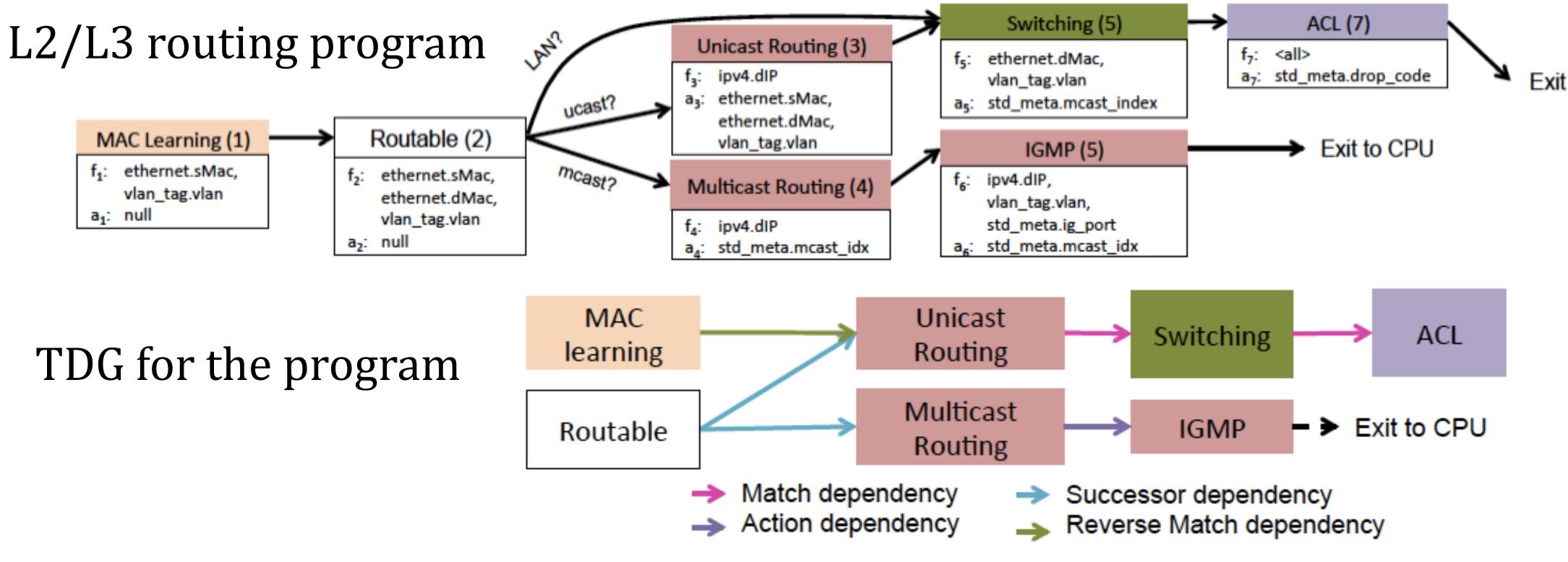

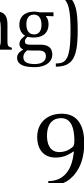

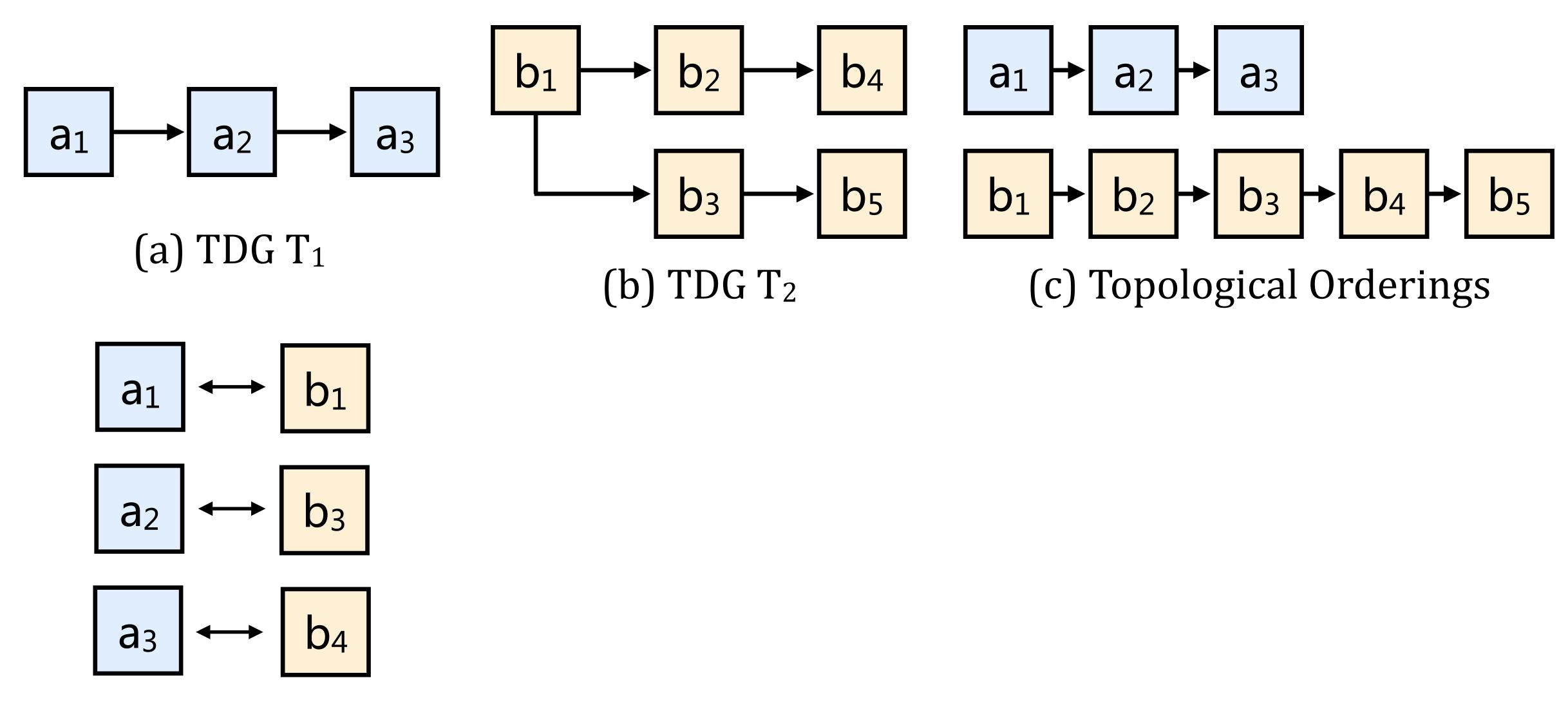

## **Table Dependency Graph (TDG)**

## Universal intermediate representation of data plane programs $T=(V_T, E_T)$ : a node in $V_T$ is an MAT; an edge in $E_T$ is an MAT dep

Figures extracted from "Compiling Packet Programs to Reconfigurable Switches", NSDI 2015

## **Table Dependency Graph (TDG)**

Background | Problems | Challenges | Design | Evaluation | Summary

## Universal intermediate representation of data plane programs $T=(V_T, E_T)$ : a node in $V_T$ is an MAT; an edge in $E_T$ is an MAT dep

Motivation#1: Requirement for reducing resource usage

Background | Problems | Challenges | Design | Evaluation | Summary

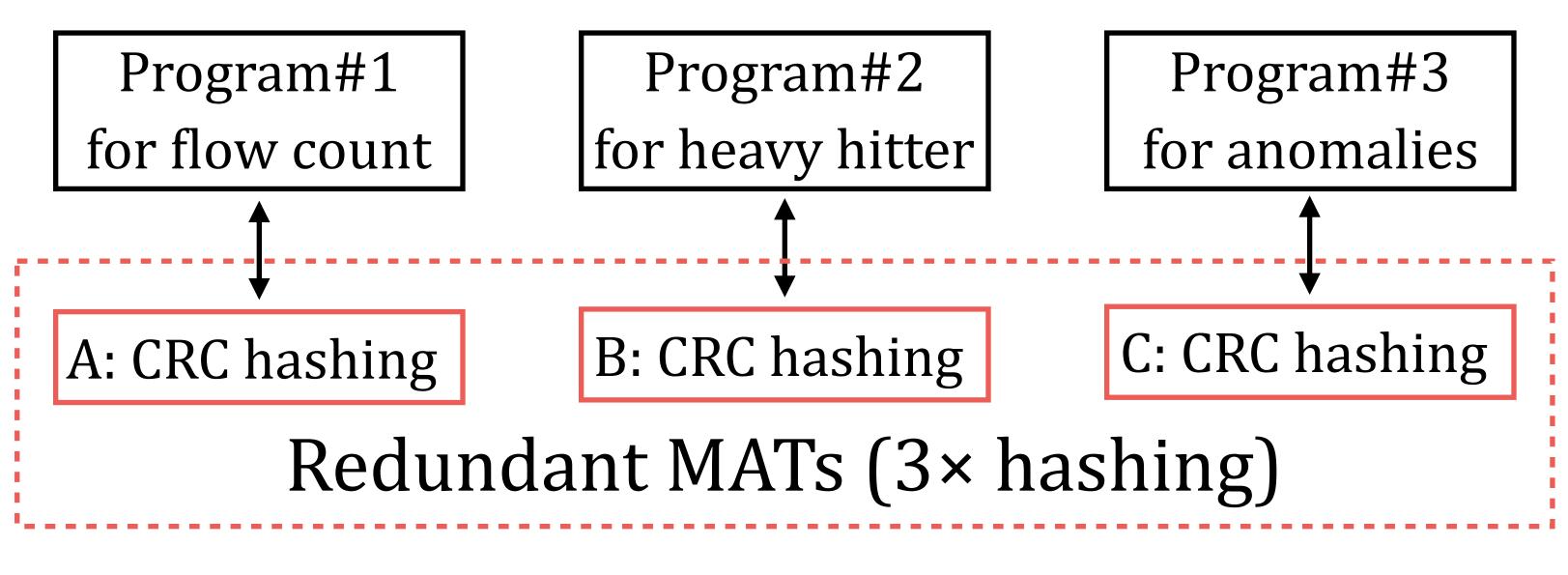

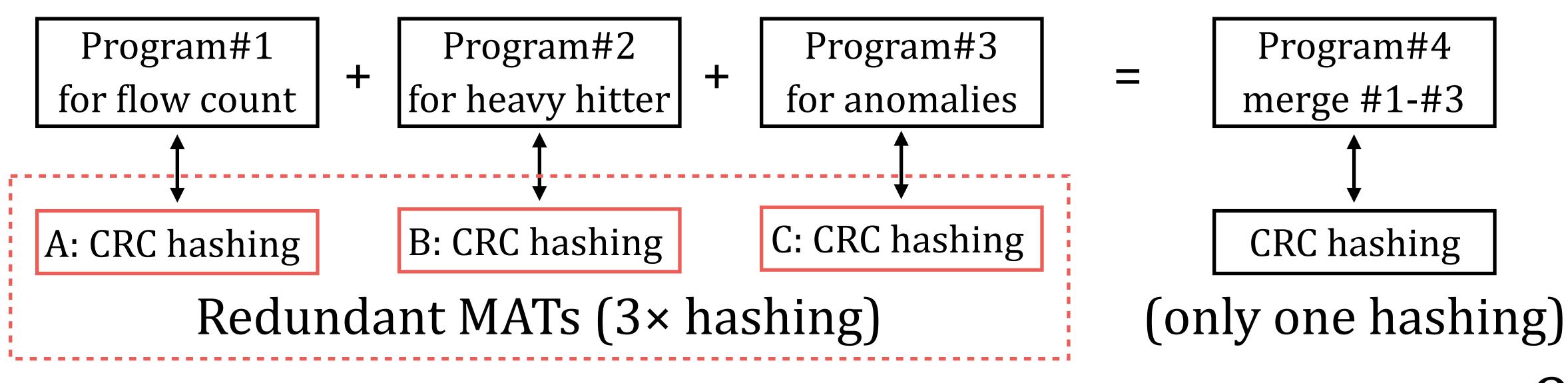

### Motivation#2: Occurrence of redundant MATs among programs

Motivation#1: Requirement for reducing resource usage

In Software-defined Measurement (SDM):

Program#1 for flow count

Program#2 for heavy hitter

Background | Problems | Challenges | **Design** | Evaluation | Summary

- Motivation#2: Occurrence of redundant MATs among programs

Program#3 for anomalies

Motivation#1: Requirement for reducing resource usage

In Software-defined Measurement (SDM):

- Motivation#2: Occurrence of redundant MATs among programs

Motivation#1: Requirement for reducing resource usage

In Software-defined Measurement (SDM):

- Motivation#2: Occurrence of redundant MATs among programs

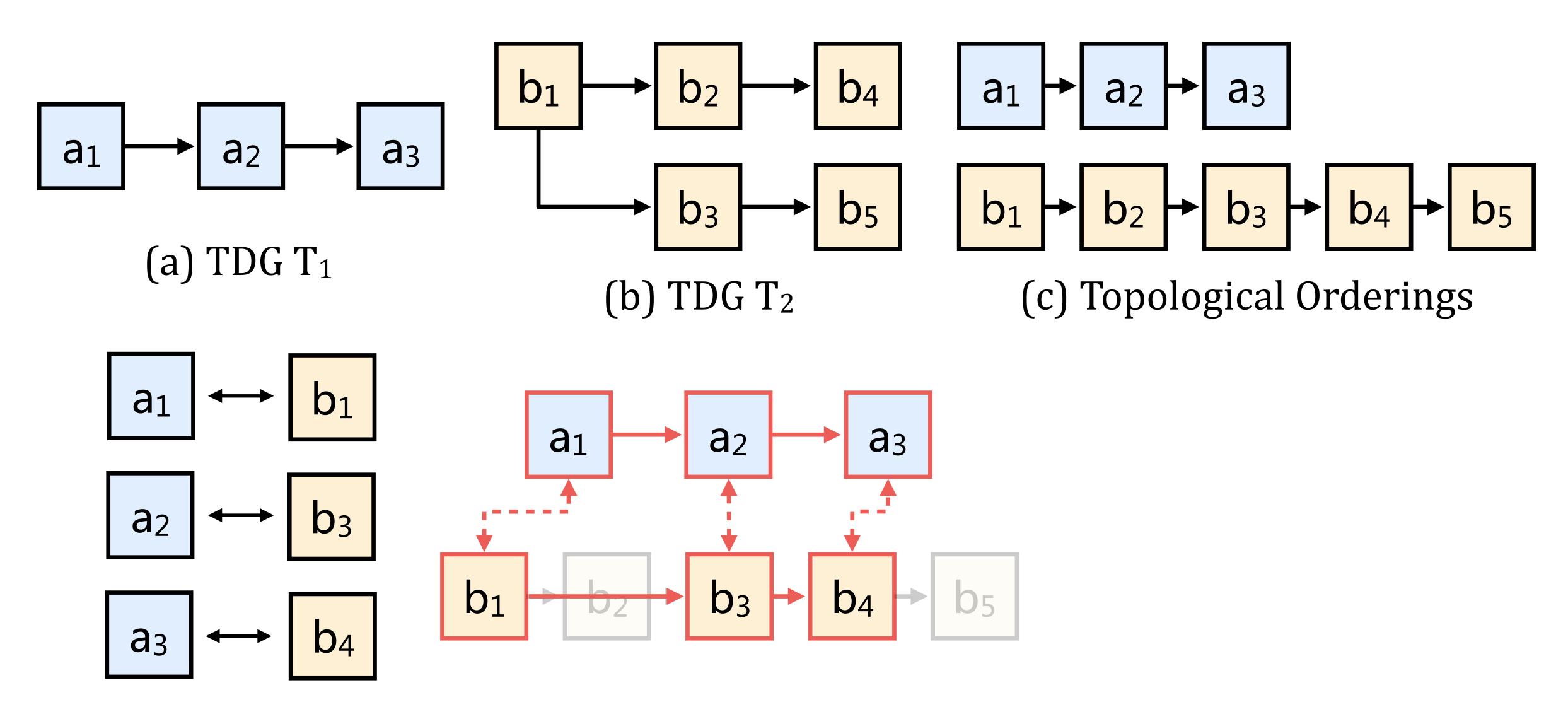

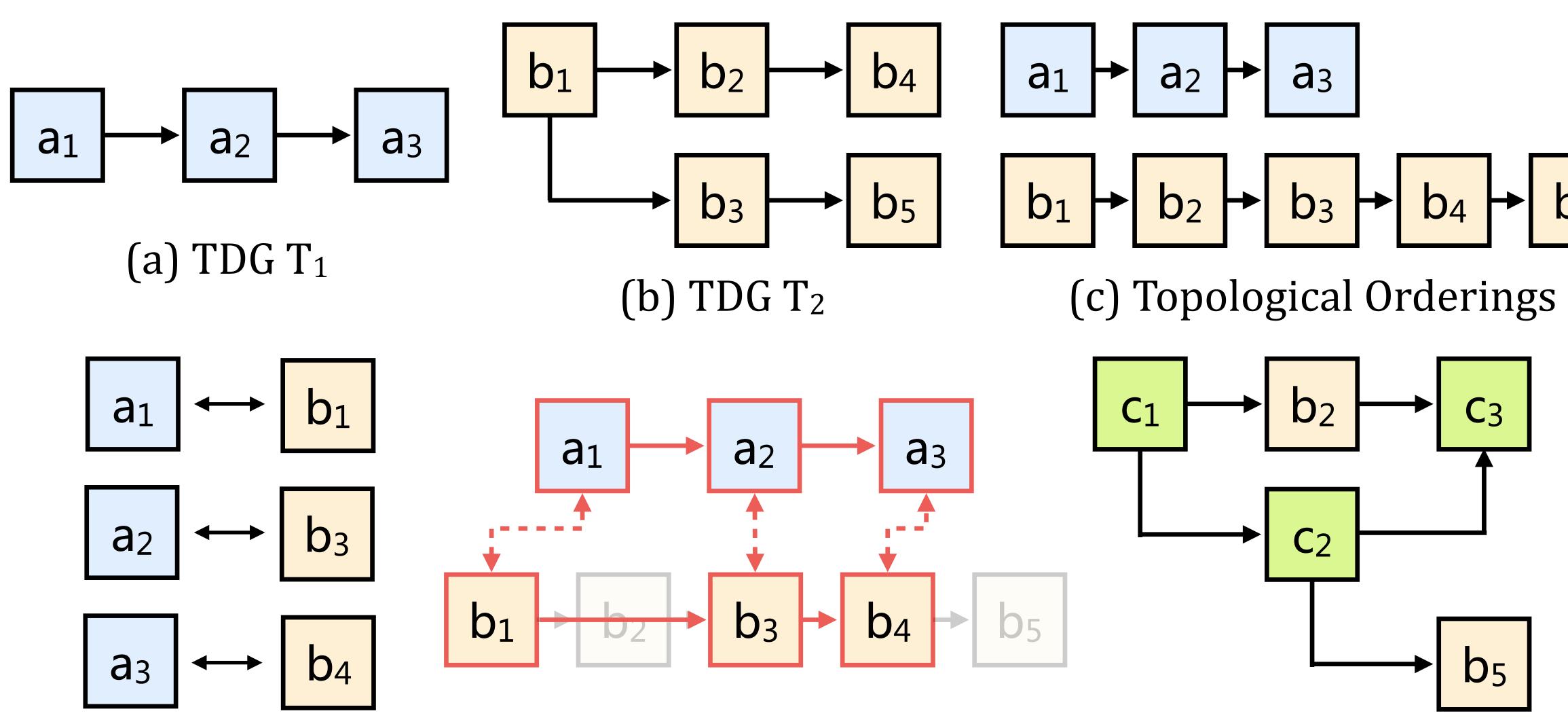

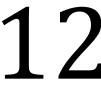

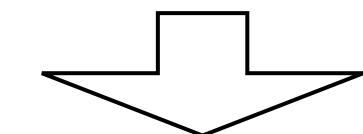

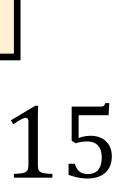

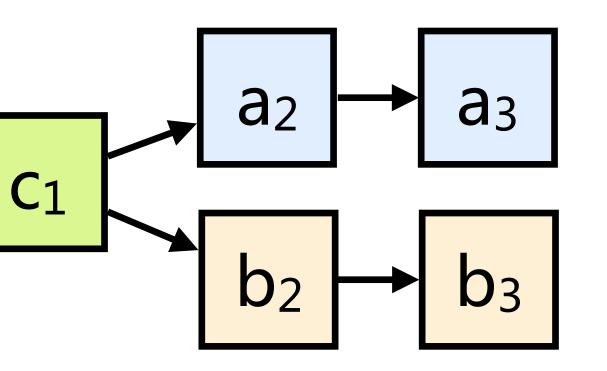

# **Program Merging for Resource Efficiency** Algorithm based on longest common subsequence (LCS) **Input:** n TDGs **Output:** a compound TDG, T<sub>m</sub> **Workflow:** n-1 iterations; each iteration takes 2 TDGs to merge

(d) Pairs of Redundant MATs

1

(d) Pairs of Redundant MATs (e) Longest Common Subsequence (LCS)

1

(d) Pairs of Redundant MATs (e) Longest Common Subsequence (LCS)

(f) Merging  $T_1$  and  $T_2$ into TDG  $T_m$

1

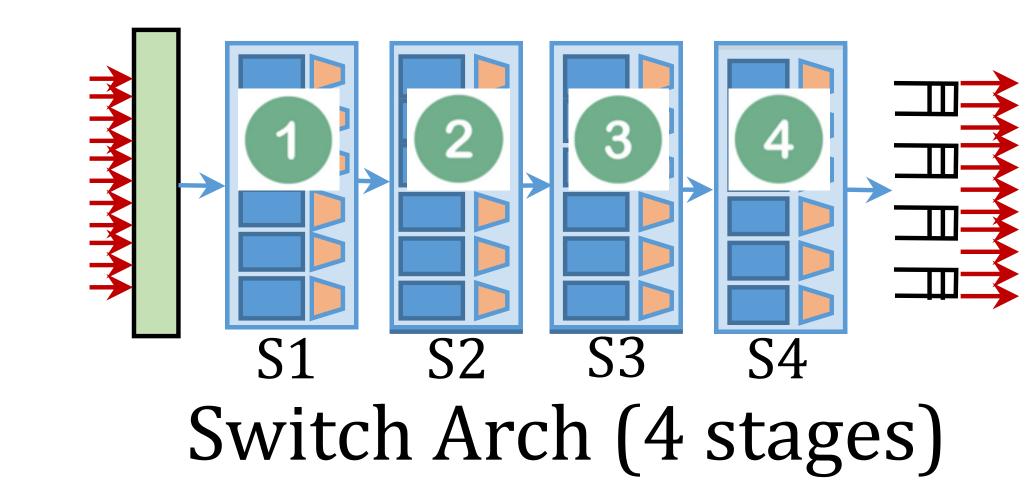

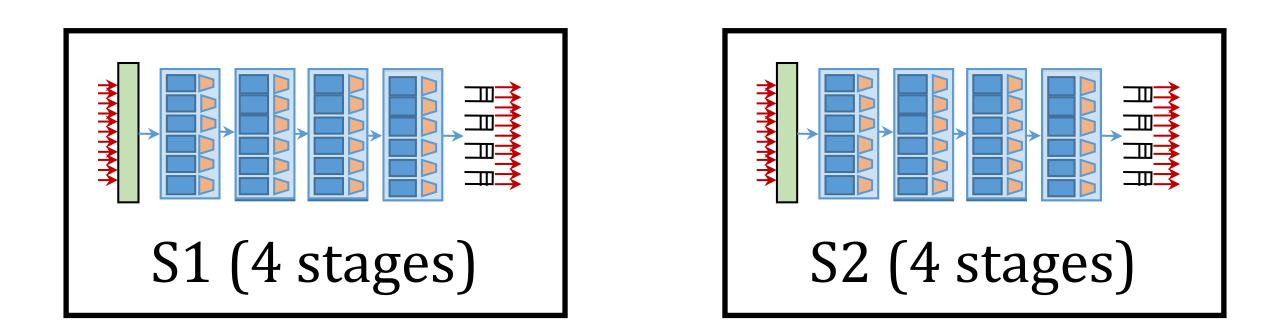

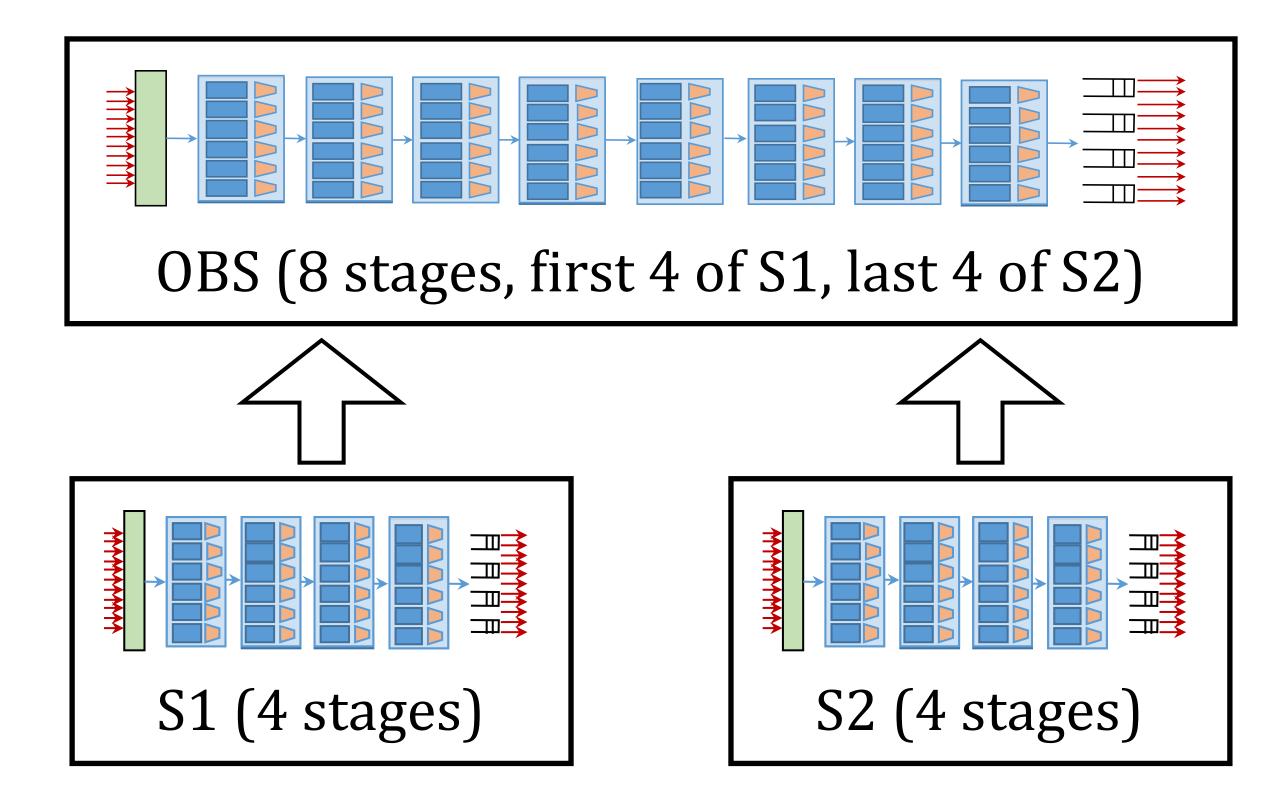

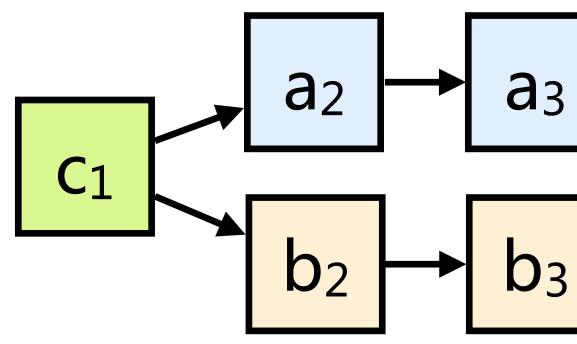

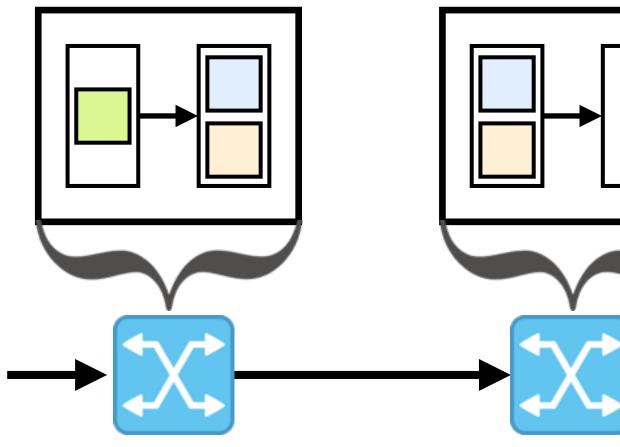

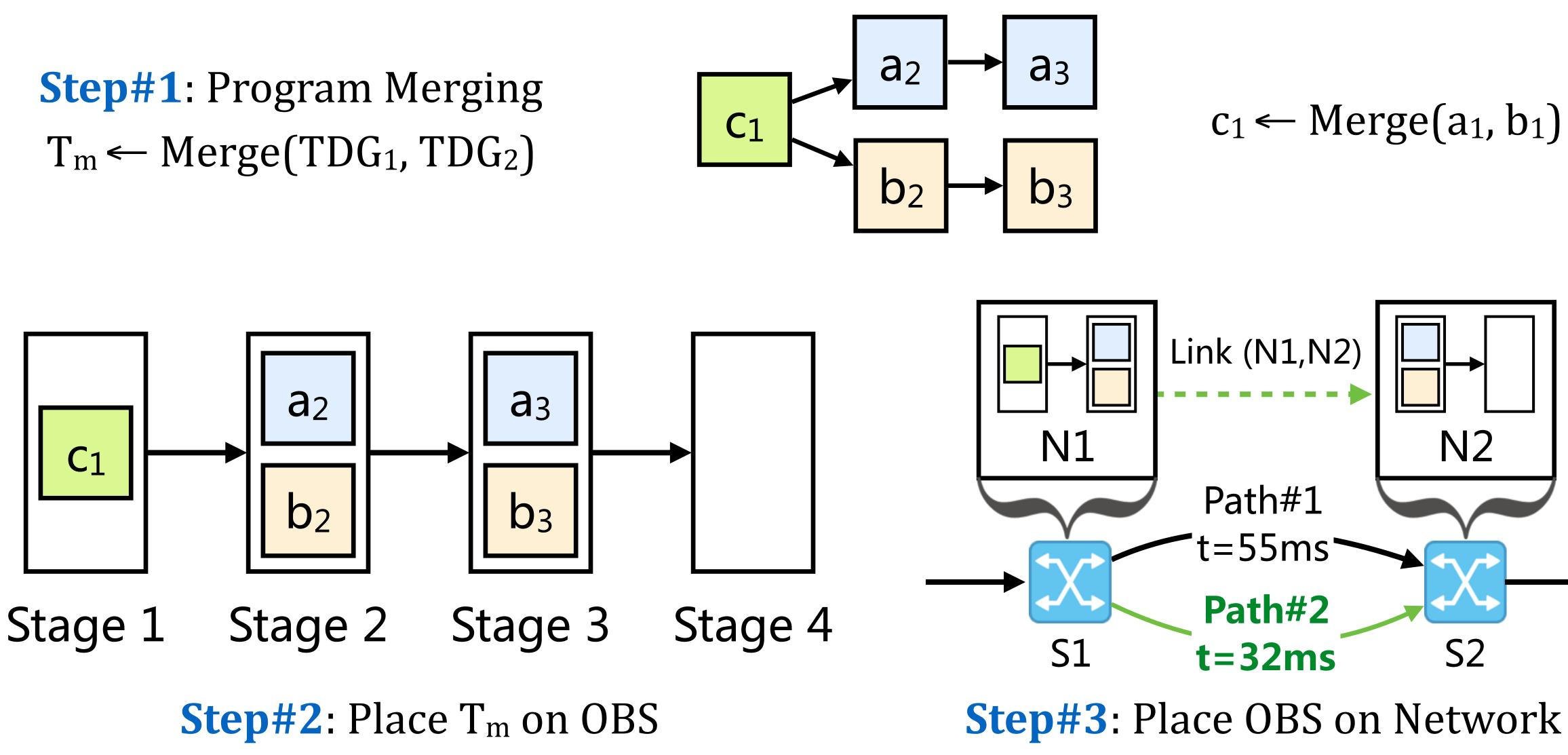

## **One Big Switch (OBS) Abstraction**

### To place $T_m$ , SPEED abstracts substrate network as an OBS

## **One Big Switch (OBS) Abstraction**

To place T<sub>m</sub>, SPEED abstracts substrate network as an OBS

Background | Problems | Challenges | Design | Evaluation | Summary

## Consolidate all stages of all programmable switches

# **One Big Switch (OBS) Abstraction** To place T<sub>m</sub>, SPEED abstracts substrate network as an OBS Property#1: Separate heterogeneous constraints in two phases

Property#2: In a phase, one obj and one type of constraints

# **One Big Switch (OBS) Abstraction** To place T<sub>m</sub>, SPEED abstracts substrate network as an OBS Property#1: Separate heterogeneous constraints in two phases Property#2: In a phase, one obj and one type of constraints Benefit#1: Simplify program deployment Benefit#2: Achieve multi-objective deployment

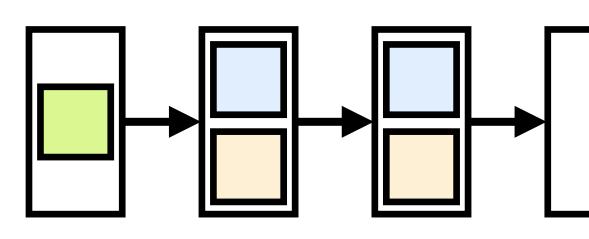

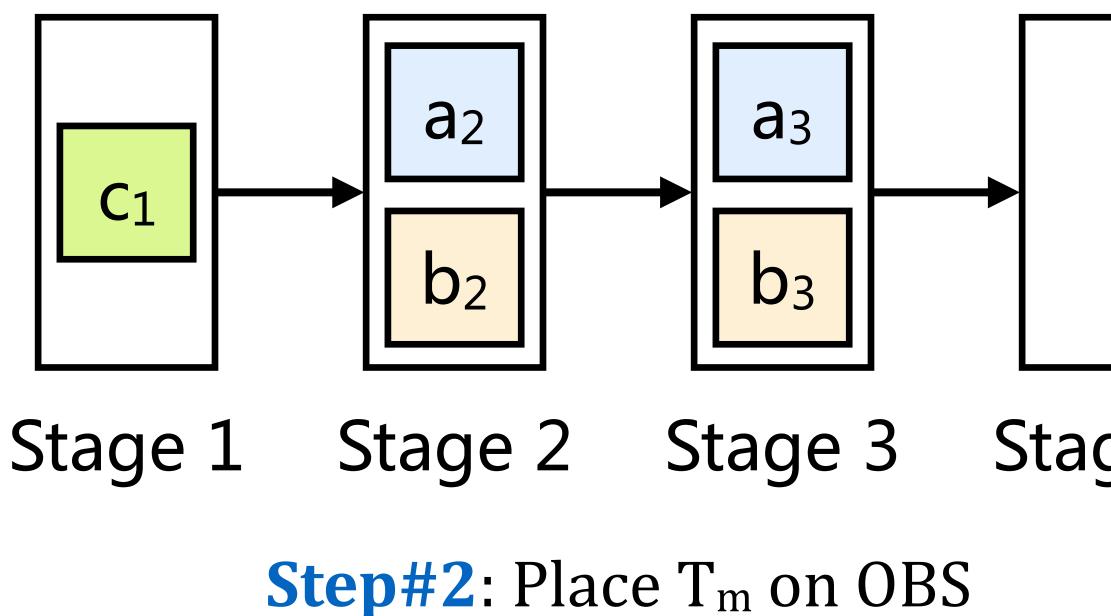

**One Big Switch (OBS) Abstraction** To place T<sub>m</sub>, SPEED abstracts substrate network as an OBS Property#2: In a phase, one obj and one type of constraints **Benefit#1**: Simplify program deployment **Benefit#2**: Achieve multi-objective deployment Phase#1: TDG placement on OBS Phase#2: OBS placement on network

- Property#1: Separate heterogeneous constraints in two phases

- Program deployment in SPEED

Phase#1: TDG Placement on OBS Formulate as ILP: **Goal**: For MAT u of T<sub>m</sub>, place u on an OBS stage v **Obj**: min (# occupied OBS stages) **C#1**: Per-stage resource limitation **C#2**: MAT dependencies (i.e., edges of T<sub>m</sub>) Solve ILP using Gurobi solver [1]

[1] Gurobi solver: https://www.gurobi.com/ Background | Problems | Challenges | Design | Evaluation | Summary

### Compound TDG T<sub>m</sub>

**OBS** Stages

**Phase#2: OBS Placement on Network** Formulate as ILP: **Goal**: For OBS stage u, place u on a real stage v **Obj**: max (throughput) | min (latency) **C#1**: One-to-one mapping **C#2**: Performance metrics Solve ILP using Gurobi solver [1] [1] Gurobi solver: https://www.gurobi.com/

Background | Problems | Challenges | Design | Evaluation | Summary

**OBS** Stages

Network

## Example: Software-defined Measurement (SDM)

SDM deploys two measurement tasks via SPEED:

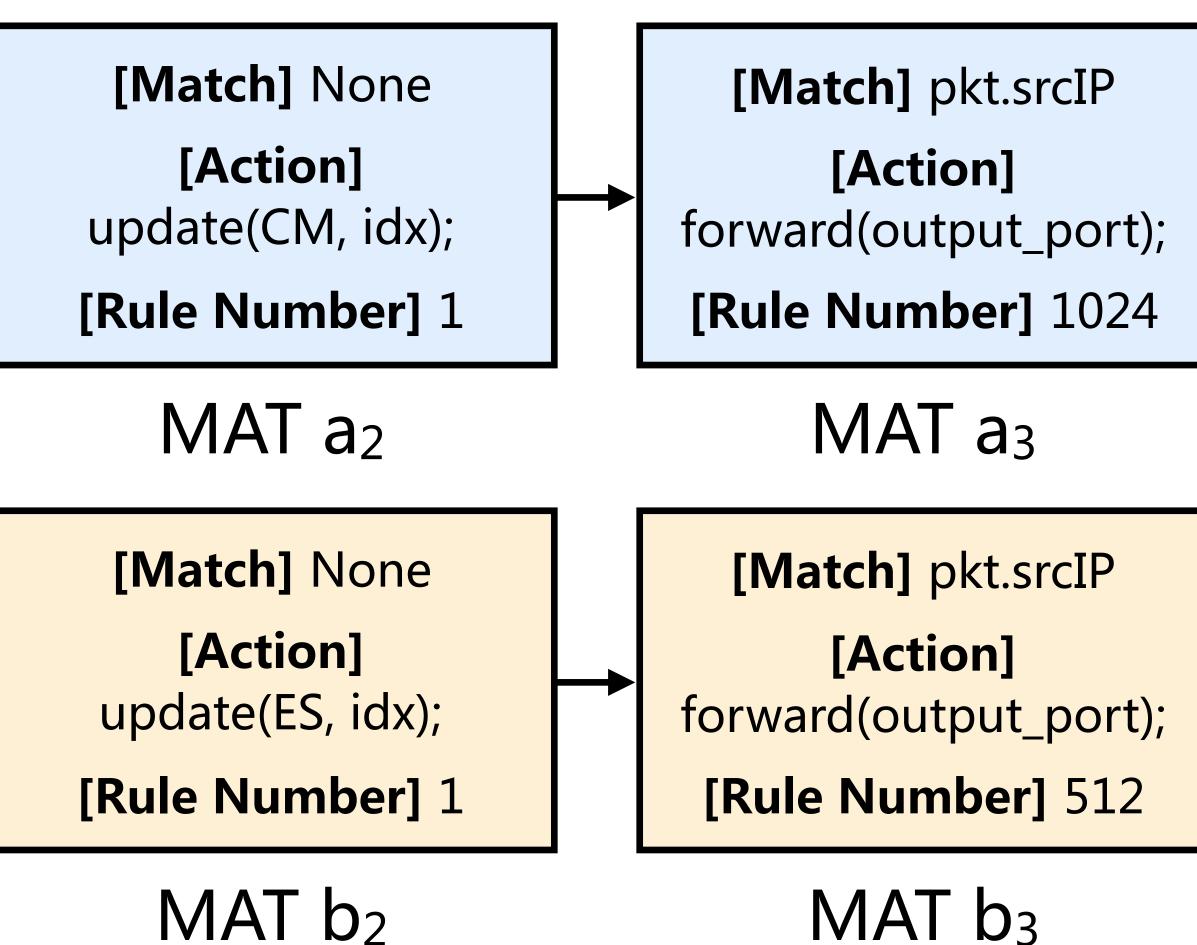

TDG<sub>1</sub> of Task#1 [Match] None

[Action] idx = crc32(pkt.srcIP);

[Rule Number] 1

MAT a<sub>1</sub>

[Match] None

**[Action]** idx = crc32(pkt.srcIP);

[Rule Number] 1

$\text{MAT} \ b_1$

TDG<sub>2</sub> of Task#2

**Step#1**: Program Merging  $T_m \leftarrow Merge(TDG_1, TDG_2)$

Background | Problems | Challenges | Design | Evaluation | Summary

### $c_1 \leftarrow Merge(a_1, b_1)$

### Stage 4

**Evaluation**

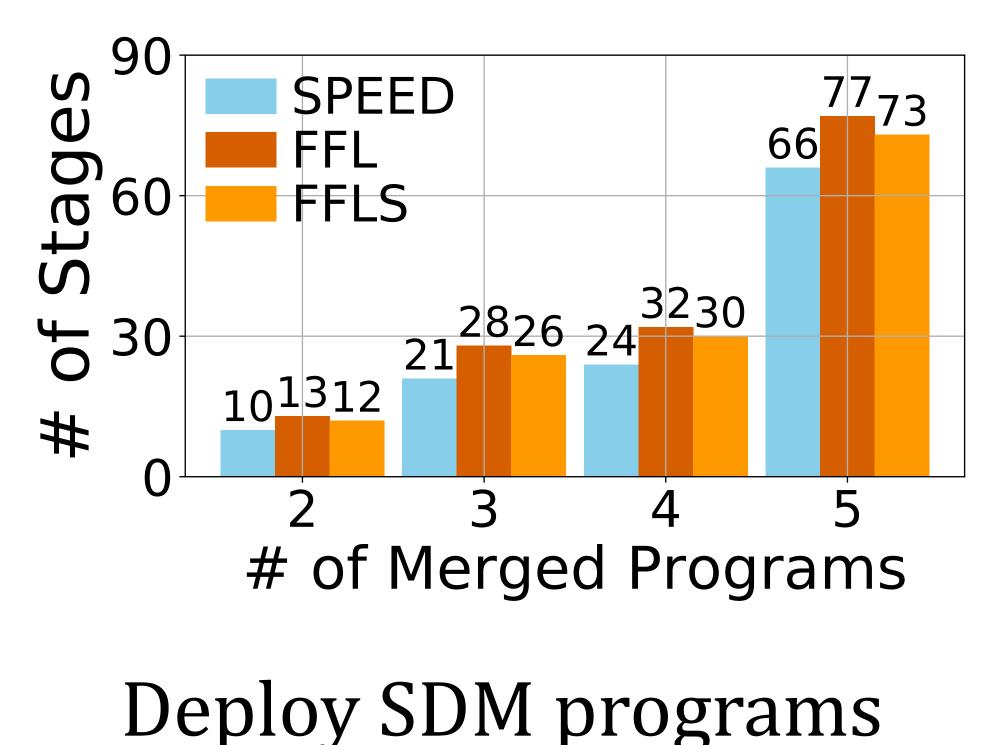

Workload: 10 real programs (5 SDM, 5 switch.p4)

(1) Can SPEED achieve resource efficiency?

- **Testbed**: Sender <=> Tofino <=> Receiver; **Simulator**: Mininet

- **Comparison**: FFL, FFLS (NSDI'15), Heuristics (BFS, NodeRank)

- (2) Can SPEED achieve high packet processing performance?

- More results can be found in our paper :-)

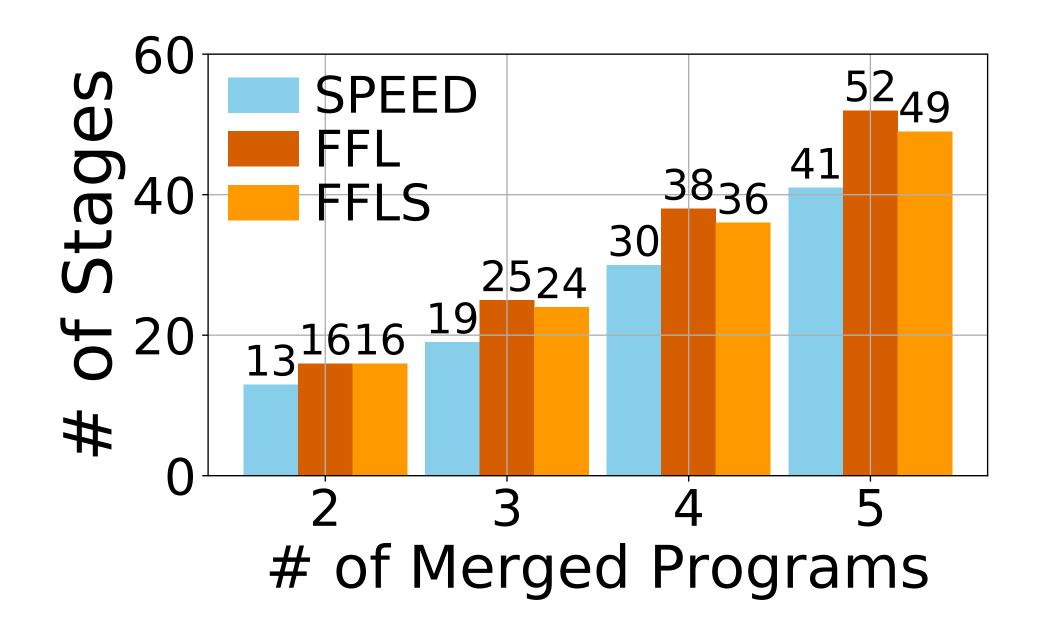

## **Can SPEED achieve resource efficiency?**

# Yes! SPEED reduces number of

Background | Problems | Challenges | Design | Evaluation | Summary

Deploy switch.p4 programs

Yes! SPEED reduces number of switch stages by up to 25%

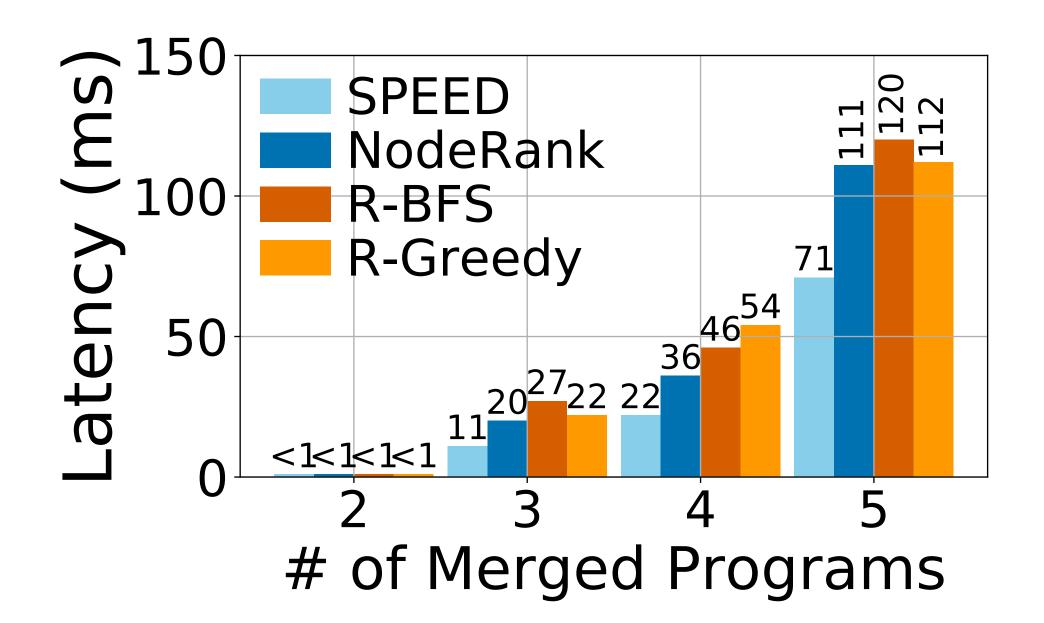

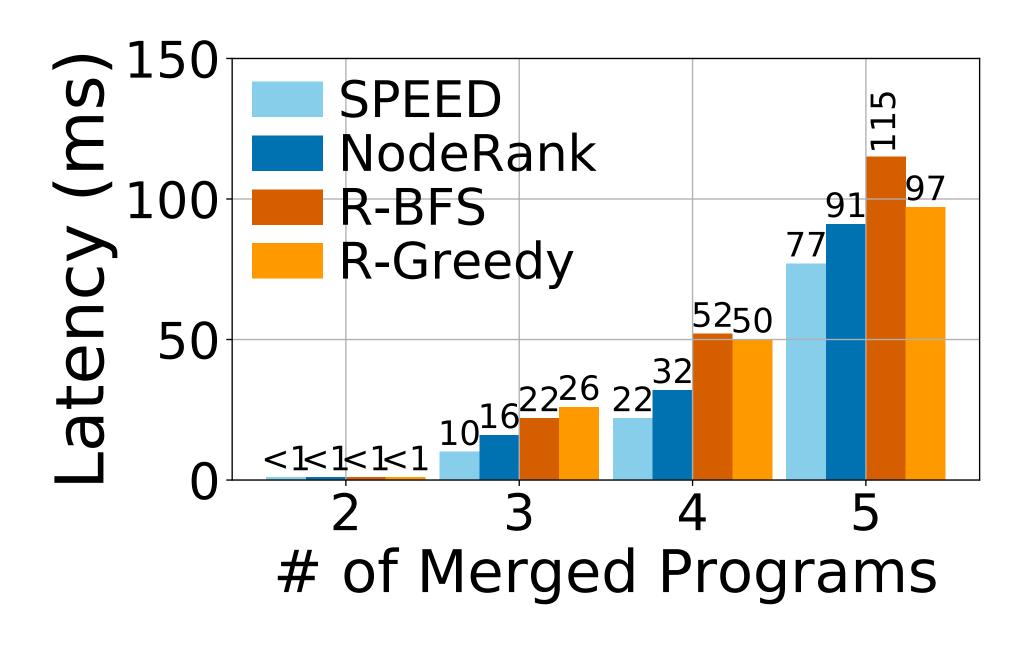

## **Can SPEED achieve high performance?**

### AboveNet topologic

### Yes! SPEED achieves 14%-59% latency reduction

Background | Problems | Challenges | Design | Evaluation | Summary

### Internet2 topologic

(1) TDG, (2) program merging, (3) OBS-based placement

Evaluation on 10 real-world data plane programs:

- SPEED: Resource-Efficient and Performant Program Deployment

- (1) save up to 25% switch stages; (2) reduce latency by 14%-59%

# Thank you very much!

**Xiang Chen**, Hongyan Liu, Qun Haifeng Zho

- Xiang Chen, Hongyan Liu, Qun Huang, Peiqiao Wang, Dong Zhang,

- Haifeng Zhou, Chunming Wu

- Email: wasdnsxchen@gmail.com Page: wasdns.github.io